Open the current project with Quartus with the Makefile.opt/intelFPGA/18.0/embedded/embedded_command_shell.sh We can let Quartus Prime software select a specic. Choose the Cyclone series device family for your DE-series board. 5.We have to specify the type of device in which the designed circuit will be implemented.

Choose the device family and a specic device.

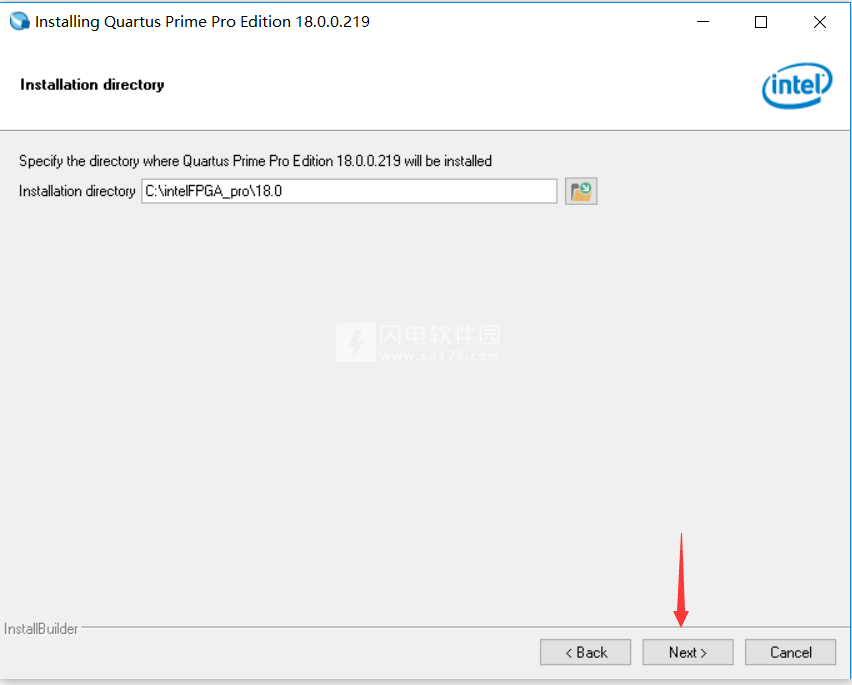

#QUARTUS 18.1 WINDOWS 10#

Tested host machine: Ubuntu 18.04 and Windows 10 Repository ¶ Description These instructions have been tested with Quartus Prime 18.1 Please note that the project can be built using the normal flow of Quartus/Platform Designer if that is desired. The reference project to the MitySOM-5CSx Development Kit utilizes GNU make for building the FPGA from the command line. The project also uses the Altera Source and Probe block for controlling signals on the partial HSMC connector for debug purposes. mm_clock_crossing_bridge - Avalon-MM Clock Crossing Bridge - Lets the HPS-to-FPGA bridge, running at 100Mhz, talk to the FPGA DDR Controller, running at 150Mhz.Description: Software Altera Quartus Prime or recently Intel Quartus. clk_100Mhz - Clock Source - Allows for inputting the CLK2DDR signal into the Qsys. Intel Quartus Prime Standard Edition 18.1 v18.1.0.625 (圆4).fpga_ddr - DDR3 SDRAM Controller with UniPHY - This is the DDR controller for the DDR RAM that is attached to the FPGA, in the example it is then routed to the HPS so the HPS can access it from the HPS-to-FPGA AXI Bridge.

#QUARTUS 18.1 FULL#

hsmc_in_1 - PIO - This is a parallel I/O block that is connected to part of the full HSMC Connector.

#QUARTUS 18.1 32 BIT#

sysid_qsys - System ID Peripheral - This basic block stores a 32 Bit system ID and the date the FPGA was built that can be read from the HPS.The FPGA design heavily uses Qsys for connecting functional blocks together and contains the following Qsys blocks: The provided FPGA images are given as a reference to how the FPGA can be used in unison with the HPS.